PCIe学习(一)

PCIe学习(二)

PCIe学习(三)

PCIe学习(四)

PCIe学习(五)

4.2.4 链路初始化和训练

需要在训练过程中确定:

- 链路宽度

- 链路速率

- Lane 反转

- Lane 极性

链路训练完成:

- 链路速率协商

- 字段锁定

- Lane 极性

- 字符锁定(Gen 1/2)或块锁定(Gen 3/4/5)

- Lane 排序

- 链路宽度协商

- Multi-Lane 链路的 Lane 间相位补偿(de-skew)

4.2.4.1 训练序列(TS1,TS2)

训练序列由有序集组成,用于初始化字段对齐、符号对齐和交换物理层参数。当数据速率为 2.5 GT/s 或 5.0 GT/s 时,有序集不会被加扰;当数据速率为 8.0 GT/s 或更高时,有续集可以加扰,也可以不加扰,取决于具体有续集类型,遵守 4.2.2.4 章节的规则。

训练序列(TS1,TS2,Modified TS1,Modified TS 2)是连续传输的,只能插入 SKP 有序集,或者对于 2.5GT/s 以外的数据速率只能插入 EIEOS 有序集。

TS1/TS2 等有续集定义请直接参考 spec。

4.2.4.2 备用协议协商

在 128b/130b 编码中,PCIe PHY 可以支持替代协议。替代协议被定义为使用 PCIe PHY 层的非 PCIe 协议。

这里暂时先跳过。

4.2.4.3 电气空闲序列(EIOS)

发送方在进入电气空闲前,必须在链路上发送电气空闲有序设置序列(Electrical Idle Ordered Set Sequence,EIOSQ)。如果当前数据速率为 2.5 GT/s、8.0 GT/s、16.0 GT/s 或 32.0 GT/s,则将电空闲有序集序列(EIOSQ)定义为一个 EIOS;如果当前数据率为 5.0 GT/s,将其定义为两个连续的 EIOS。

当使用 8b/10b 编码时,EIOS 是一个 K28.5(COM),后面跟着三个 K28.3(IDL)符号。当使用 128b/130b 编码时,EIOS 是有序集块。

只有在 2.5 GT/s 以外的速度下运行时,才会传输电气空闲退出有序集(EIEOS)。EIEOS 是周期性传输的低频模式,有助于确保接收机的电空闲退出电路能够检测到电气空闲的退出。当使用 128b/130b 编码时,它也用于块对齐。电空闲退出有序集序列(EIEOSQ)包括用于 32.0 GT/s 及以上数据速率的两个连续 EIEOS 和用于 5.0 GT/s、8.0 GT/s 和 16.0 GT/s 的一个 EIEOS。32.0 GT/s 的两个 EIEOS 必须背靠背且不能被打断,才能被视为连续的并形成 EIEOSQ。

电气空闲退出有续集定义:

这里有几个小节不贴了,神烦~~

接来的小节简单介绍一下

4.2.4.11 链路宽度和 Lane 序列号协商

PCIe 链路支持 1, 2, 4, 8, 12, 16, 32 Lane,也被称为 x1, x2, x4, x8, x12, x16, x32(实际中并没有 x12 和 x32,至少我没见过)。所有的 Lane 必须以相同速率传输。

链路宽度和 Lane 序列号协商过程用来确定链路数量和编号,以及属于链路的 Lane 数量和编号;不是有效链路的 Lane 退出协商,以成为单独的链路或保持在电气空闲中。

4.2.4.12 Lane-to-Lane 相位补偿

一条链路的所有 Lane 是独立传输的,Lane 与 Lane 之间不可避免地存在时钟偏移。

8b/10b 编码时,Lane 间相位补偿机制可以使用:

- 接收到的 TS1 或 TS2 有序集的 COM 符号

- 接收到的 EIEOS 有续集的 COM 符号

- FTS 序列后第一个收到的 SKP 有序集的 COM 符号

- 当不使用 SRIS(Separate Reference Clocks With No SSC)时,在训练序列期间接收的 SKP 有序集的 COM 符号

128b/130b 编码时,Lane 间相位补偿:

- 收到的 SDS 有序集

- 接收到的 EIEOS 有序集(退出 L0s 时除外)

- 退出 L0s 时 FTS 有序集之后收到的第一个 EIEOS 有序集

- 当以 8.0 GT/s 运行时,收到的 SKP 有序集

- 当以 16.0 GT/s 或更高的数据速率运行时,FTS 序列后第一个收到的 SKP 有序集

- 当以 16.0 GT/s 或更高的数据速率运行时,收到的 SKP 有序集,但以下情况除外:退出训练序列或被 EDS 分隔的两个 SKP 有序集由

4.2.4.13 Lane vs. Link Training

链路初始化过程将端口的非关联 Lane 构建为形成链路的关联 Lane。为了将 Lane 正确配置为所需的链路,TS1 和 TS2 有序集必须在所有 Lane 上将相应的字段(符号 3、4 和 5)设置为相同的值。

4.2.5 LTSSM(Link Training and Status State Machine)

PCIe 链路在上电后,首先要完成链路训练,然后设备才能进行正常的被设置和使用。

所谓训练,就是要让链路两端建立起通信的桥梁。完成这一工作的就是 LTSSM(Link Training and Status State Machine)。

为了完成这个艰巨的任务,LTSSM 需要做的事情包括:

- 比特锁定(Bit Lock):对于连续不断的电平信号,接收端需要知道采样的时刻,才能进一步确定采到的是 1 还是 0。发送端是按照自己本地的时钟去发送,接收端的时钟与发送端的时钟完全不同步,这是接收端需要 CDR(Clock Data Recovery)电路从接收到的比特流中恢复出发送端的时钟。

- 字符锁定(Symbol Lock):对于 Gen 1/2,接收端虽然完成了比特锁定,能正确从比特流中采样到每个比特,但此时仍然不知道比特流的边界在哪里,也就是不知道如何对比特流进行断句。这就需要发送端不断的发送 TS1/2 有续集,接收端需要从比特流中识别出特定的模式(比如 COM 字符),也就知道该怎么断句比特流了。

- 块锁定(Block Lock):对于 Gen 3,没有了控制字符,需要借助 EIEOS 有续集(00h 和 FFh 交替)作为特定模式,帮助完成块锁定。

- 链路宽度(Link Width):确定链路有多少 Lane 可用

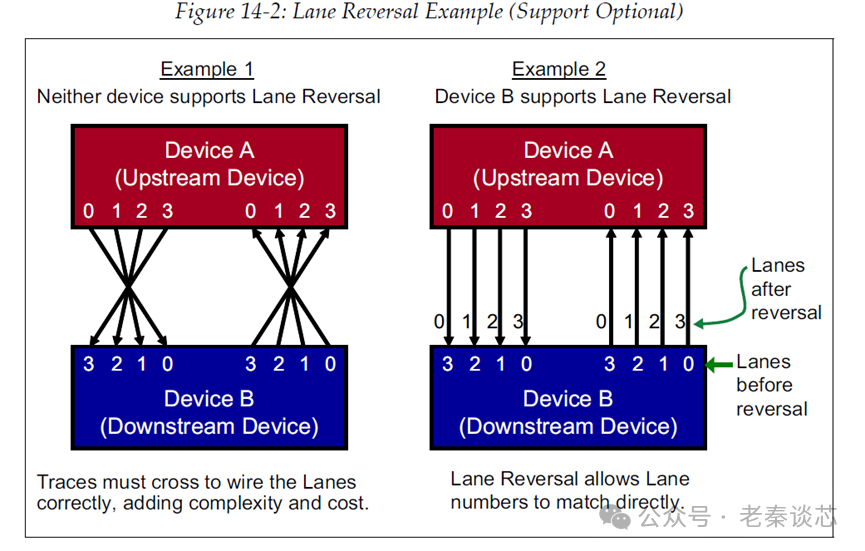

- Lane 反转(Lane Reversal):对于多 Lane 的链路,需要 Lane 0 对 Lane 0,Lane 1 对 Lane 1 这样严格的对应关系。这样难免会对板级设计带来约束。如果设备能在内部改变对应关系,则可以避免这种约束。Lane 反转不是强制功能。

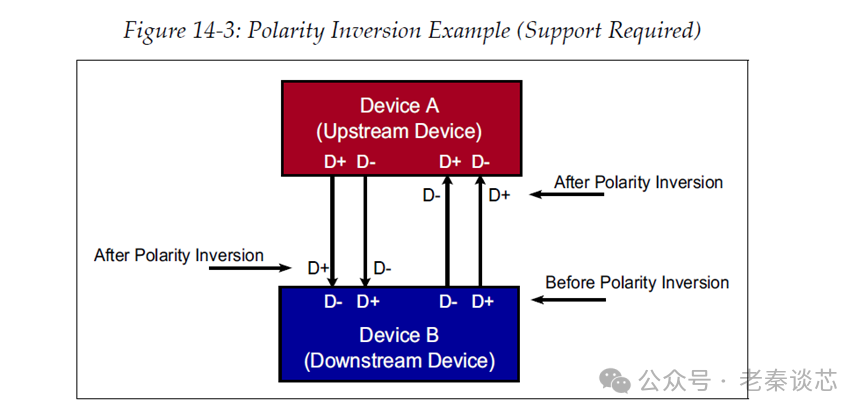

- 极性反转(Polarity Inversion):PCIe 是差分传输,在一个传输方向上有 D+和 D-两条线来组成一个 Lane。在板级设计时,需要 D+对 D+,D-对 D-这样连接。如果是 D+对 D-连接,需要链路的一方在内部做信号极性反转。这一过程链路双方是通过 TS1/2 有续集协商完成。

- 链路数据速率(Link Data Rate):PCIe 的最低传输速率是 2.5GT/s,如果链路双方支持更高的速率,需要在链路训练时通知对方,最终将链路训练到支持的最高速率。

- Lane 间校正(Lane‐to‐Lane De‐skew):对于多 Lane 链路,每条 Lane 在电路板上的传输不可能做到完全一样,所以接收端在每条 Lane 上接收到的信号必然会有快有慢,这个问题也称作信号偏斜(Signal Skew)。接收端必须要对不同 Lane 做一些补偿,以减轻板级设计者的压力。

LTSSM 的状态转换图如下所示。LTSSM 共有 11 个状态,每个状态下面有若干细分状态。这 11 个状态可以分为五类:

- 链路训练状态。当设备的复位信号被释放后,LTSSM 经历状态转换过程为 Detect -> Polling -> Configuration -> L0。在 L0 状态,链路可以正常传输。

- 重新训练状态,也叫恢复(Recovery)状态。当链路从低功耗状态切换回 L0,或者是链路宽度或速度需要改变时,需要重新训练。

- 软件驱动的电源管理状态。软件可以控制设备进入低功耗状态(D1,D2,D3hot,D3Cold),链路对应也要进入低功耗状态 L1 或者 L2。

- 活动状态电源管理(Active-State Power Management,ASPM)状态。在链路上没有有效传输的时间段内,允许 ASPM 硬件切换链路到低功耗状态(L0s 或者 ASPM L1)。

- 其它状态。包括 Disable,Loopback,Hot Reset。

LTSSM 的具体 11 个状态如下:

- Detect:此状态是设备复位后的初始状态,目的是检测链路远端是否存在设备

- Polling:此状态适用于测试设备是否符合电压和时序规范,链路的发送端不断发送 TS1 和 TS2 有续集(2.5GT/s 速率),接收端通过这些有续集完成比特锁定,字符锁定,Lane 极性反转等等

- Configuration:在此状态,链路两端通过协商机制确定 Lane 宽度,分配 Lane 编号,Lane 反转,Lane 间补偿等

- Recovery:有很多种原因会导致 LTSSM 进入此状态,比如在链路 L0 时发生错误,链路从 L1 切换回 L0 等等,在此状态下,需要发送 FTS 序列

- L0:正常工作状态,初次进入 L0 的链路速率是 2.5GT/s,如果两端支持更高速率,需要进入 Recovery 在更高速率下进行重新训练

- L0s:低功耗状态,提供灵活的低功耗管理,从 L0s 切换回 L0 需要的时间更短。从 L0 转移到 L0s,需要发送 EIOS;退出 L0s,需要发送 FTS

- L1:比 L0s 激进的低功耗状态

- L2:比 L1 激进的低功耗状态,此状态下,发射机和接收机关闭,主要供电电源和时钟关闭,仅有辅助电源开启

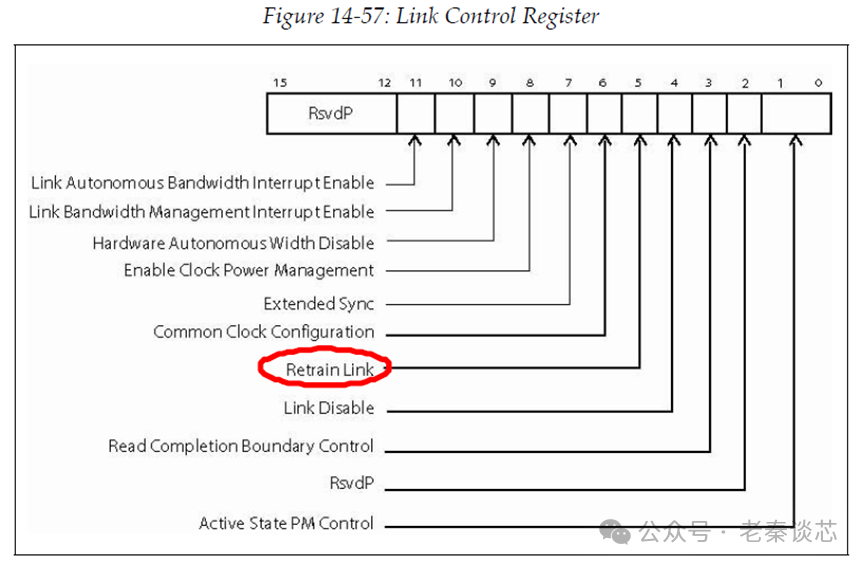

- Disable:此状态允许禁用已配置的链接。在这种状态下,发射端处于电空闲状态,而接收端处于低阻抗状态。软件通过设置链路控制寄存器中的 Disable 位来命令设备执行此操作。然后,该设备发送 16 个 TS1,其中在 TS1 训练控制字段中设置了 Disable Link 位。接收端在接收到这些 TS1 时被禁用

- Loopback:此状态用于测试和故障隔离,基本操作是,环回主设备将在训练控制字段中设置了 Loopback 位的 TS1 有序集发送给将成为环回从设备。当一个设备看到设置了 Loopback 位的两个连续 TS1 时,它会作为环回从设备进入环回状态

- Hot Reset:软件可以通过设置桥接控制寄存器中的 Secondary Bus Reset 位来重置链路。这会导致桥的下游端口发送 TS1,并在 TS1 训练控制字段中设置热复位。当接收端看到两个连续的 TS1 设置了热复位时,它必须复位其设备

上述 11 个状态中,Detect,Polling,Configuration,L0,Recovery 这几个状态较为复杂和常用。有的状态还细分出若干子状态。

Detect

此状态有两个子状态:Detect.Quiet 和 Detect.Active。

Detect.Quiet

设备在复位被释放后进入此状态(除 Function Level Reset)。发送端在电气空闲状态下启动。物理层通过置低 LinkUp 来告诉数据链路层,PCIe 的物理链路尚未准备好。

当所有 Lane 退出电气空闲,或者超过 12ms,从 Detect.Quiet 状态退出,切换到 Detec.Active 状态。

Detect.Active

在此状态下,检测链路的对端是否存在 PCIe 设备。

如果在所有 Lane 上都没有检测到有 PCIe 设备存在,则切换回 Detect.Quiet 状态。

如果检测到有 PCIe 设备存在,则切换到 Polling 状态。

Polling

此状态的主要目的是让链路两端两个设备建立沟通,了解对方在说什么。换句话说,它们需要在彼此传输的比特流上建立比特锁定和符号锁定,并解决极性反转等问题。一旦这些工作完成,每个设备都可以成功地从链路对端接收 TS1 和 TS2 有序集。

此状态有三个子状态:Polling.Active,Polling.Configuration,Polling.Compliance。

Polling.Active

在此状态下,发送端至少需要发送 1024 个连续的 TS1。链路两端的设备很可能不会同时从 Detect.Active 状态切换到 Polling.Active,因此需要连续发送 TS1 来不停向对端设备展现(Advertise)自己。发送 1024 个 TS1 需要 64us(在 2.5GT/s)。

如果在发送至少 1024 个 TS1 之后,所有检测到的通道接收到满足以下条件之一的 8 个连续训练序列,则进入 Polling.Configuration 状态:

- 接收到链路和通道设置为 PAD(Packet filler)的 TS1,Compliance Receive 位清除为 0b(符号 5 的第 4 位)。

- 接收到链路和通道设置为 PAD 的 TS1,符号 5 的 Loopback 位设置为 1b。

- 接收到链路和通道设置为 PAD 的 TS2。

如果 Link Control 2 寄存器中的 Enter Compliance 字段设置为 1b,或者如果该位是在进入 Polling.Active 之前设置的,则必须立即更改状态为 Polling.Compilance,并且 Polling.Active 中不发送 TS1。

如果在 24ms 内,及不满足进入 Polling.Configuration 状态,也不满足进入 Polling.Compilance 状态,则切换到 Detect 状态。

Polling.Configuration

发送端停止发送 TS1,开始发送 TS2。更改为发送 TS2s 的目的是向链路对端设备通告本设备已准备好进入状态机中的下一个状态。它是一种握手机制,用于确保链路上的两个设备一起通过 LTSSM。

在任何检测到的通道上接收到链路和通道设置为 PAD 的八个连续 TS2,并且自接收到一个 TS2 以来至少发送了 16 个 TS2 之后,退出当前状态,切换到 Configuration。

否则,在 48ms 超时后,切换到 Detect 状态。

Polling.Compliance

该子状态仅用于测试,并使发射机发送特定模式,以创建接近最坏情况的符号间干扰(ISI)和串扰条件,从而促进链路分析。

对于 8b/10b 和 128b/130b 编码,特定模式有不同的规定。

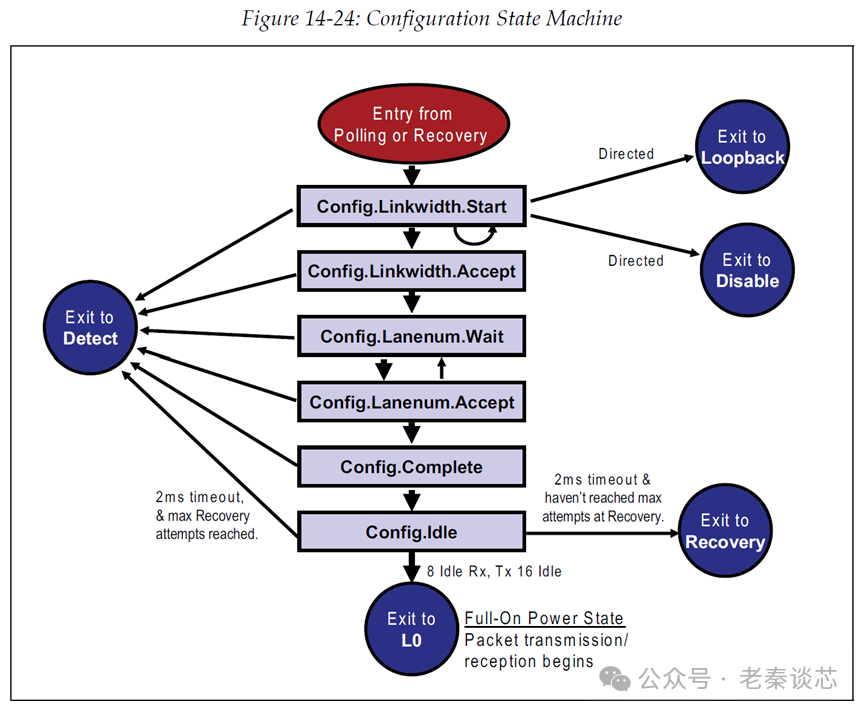

Configuration

此状态的主要目的是发现端口是如何连接的,并为其分配 Lane 编号。比如,一个 8 Lane 的设备可以连接两个 4 Lane 的设备。此时,DSP 承担“leader”角色,而 USP 承担“follower”角色。DSP 将指定 USP 的链路和 Lane 编号,USP 将简单地使用其被告知的相同值进行回复。链路和 Lane 编号在 TS1 里面的字段。

下图是一个示例,Switch 有一个 x8 的 USP,四个 x2 的 DSP,每个 DSP 对应有一个内部的虚拟桥。在实际应用时,允许将四个 DSP 合并成两个 x4 的 DSP,此时,两个内部虚拟桥将不会被使用。

Configuration 状态有六个子状态:

- Configuration.Linkwidth.Start

- Configuration.Linkwidth.Accept

- Configuration.Lanenum.Wait

- Configuration.Lanenum.Accept

- Configuration.Complete

- Configuration.Idle

六个子状态的介绍跳过。

L0

这是正常的、完全可操作的链路状态,在此状态期间,链路两端之间可以交换逻辑空闲、TLP 和 DLLP。L0 是在链路训练过程结束后立即实现的。物理层还通过设置 LinkUp 变量通知上层链路已准备好运行

如果链路速度或链路宽度发生变化,或者链路伙伴通过进入“恢复”或“电气空闲”发起操作,则进入 Recovery 状态。

Recovery

当在 Configuration.Idle 状态时,链路上出现错误的字符;或者是在 L0 状态时,需要提升链路速率至最高,等等情况,LTSSM 需要进入 Recovery 状态。

Recovery 状态是 LTSSM 中比较复杂的状态,有以下几种子状态:

- Recovery.RcvrLock:在该子状态中,允许上游端口指定下游端口在 5GT/s 下运行时应使用的去加重(De-emphasis)级别。想要将速率更改为 8.0 GT/s 并重新进行均衡的下游端口必须发送设置了 speed_change 位的 EQ TS1,并公布 8.0 GT/s 速率。

- Recovery.Equalization:该子状态用于执行 8.0 GT/s 和更高速率的链路均衡(Link Equalization)过程。

- Recovery.Speed:在该子状态,设备的发送器必须进入电气空闲,并等待接收器进入电气空闲。

- Recovery.RcvrCfg:只有在接收到至少 8 个 TS1 或 TS2 有序集(具有之前协商的相同 Link 和 Lane 编号)后,才能从 Recovery.RcvrLock 进入此状态。这意味着位和符号/块锁定已经建立,现在端口必须确定是否有任何其他项目需要在 Recovery 状态下

- Recovery.Idle:顾名思义,发送器通常会在该子状态下发送 Idles(空闲),作为切换到完全运行 L0 状态的准备。对于 8b/10b 模式,空闲数据通常在所有 Lane 上发送,而对于 128b/130b,发送 SDS 以启动数据流,然后空闲数据字符被发送到所有 Lane 上。

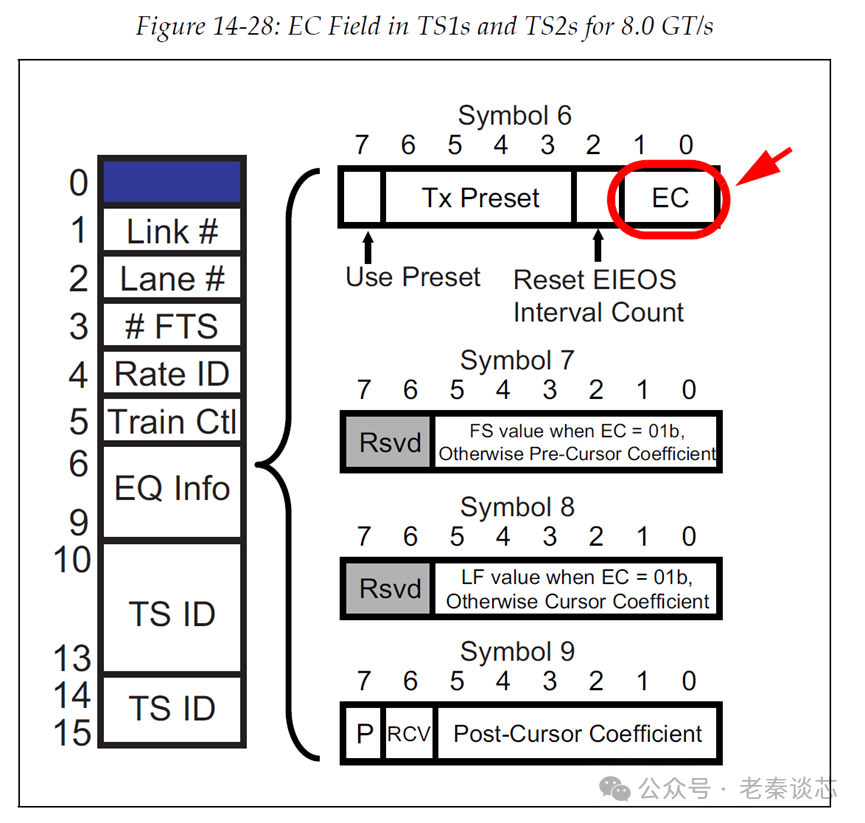

前面讲过,链路均衡过程分为四个阶段,phase 0-3。一旦速度变为 8.0 GT/s,TS1 中的 EC(Equalization Control)字段指示当前使用的均衡阶段。

接下来分析一下每个 Phase,下游端口和上游端口都需要做什么。

因为链路均衡过程是下游端口发起的,所以对于下游端口来说,没有 Phase 0。

- Phase 1 Downstream。DSP 发送具有 EC=01b 的 TS1,同时使用 Lane 均衡控制寄存器中的预设值以及与 Tx 预设字段对应的 FS、LF 和 Post‐cursor 系数字段。如果下行端口希望继续均衡过程,并且当其所有配置的 Lane 接收到两个连续的 EC=01b 的 TS1 时,下行端口将转换到 Phase 2。

- Phase 2 Downstream。下行端口在每条 Lane 上独立发送 EC = 10b 和系数设置的 TS1。当上行端口对这些变化感到满意时,它开始发送 EC = 11b 的 TS1,指示希望改变到 Phase 3。当 DSP 接收到两个像这样的连续 TS1 时,将均衡 Phase 2 Successful 状态位设置为 1b,并进入 Phase 3。

- Phase 3 Downstream。下行端口发送 EC = 11b 的 TS1,并开始独立评估每个通道的上行 Tx 设置

- Phase 0 Upstream。USP 发送 TS1(EC=00b),使用进入该状态前在 EQ TS2s 中传送的 Tx 预设值。发送的 TS1 中的均衡信息字段必须显示预设值,以及与该预设对应的 Pre‐cursor, Cursor, Post‐cursor 系数字段。当 USP 在所有配置的 Lane 上接收到 EC=01b 的两个连续 TS1 时,表明其可以识别来自下游端口的 TS1,则可以进入 Phase 1。

- Phase 1 Upstream。上游端口发送 EC=01b 的 TS1,同时使用 Phase 0 中确定的发送器设置。这些 TS1 包含 FS、LF 和当前使用的 Post‐cursor 系数值。如果 USP 在所有配置的通道接收到 EC = 10b 的两个连续 TS1,指示下游端口想要进入 Phase 2,则 USP 进入 Phase 2,并且该端口将设置均衡 Phase 1 成功状态位设置为 1b。

- Phase 2 Upstream。上行端口发送 EC=10b 的 TS1,并开始为下行端口寻找最佳 Tx 值的过程。请记住,每个通道的设置都是独立确定的。如果所有配置的 Lane 都达到其最佳设置。则 USP 进入 Phase 3,均衡 Phase 2 成功状态位将设置为 1b。

- Phase 3 Upstream。上游端口发送 EC = 11b 的 TS1,并响应来自下游端口的所请求的 Tx 值。如果没有看到两个连续的 TS1,则保持当前 Tx 预设值和系数值。然而,如果第一次接收到 EC = 11b(下游端口已进入阶段 3)的两个连续 TS1,或者接收到与上次不同的预设值或系数值,并且如果所请求的值是合法的且受支持的,则在请求它们的第二 TS1 结束后的 500ns 内更改 Tx 设置以使用它们。当下游端口对这些变化感到满意时,它开始发送 EC=00b 的 TS1,表示希望完成均衡过程。当 USP 接收到像这样的两个连续 TS1 时,将均衡 Phase 3 成功和均衡完成状态位设置为 1b。

L0s

链路低功耗状态。设备可以在硬件控制下自动进入或退出 L0s 状态,无需软件参与。

对于发射机和接收机,有不同的 L0s 子状态。

发射机有三种子状态:

- Tx_L0s.Entry:发射机发送一个 EIOS(在 5GT/s 时发送两个),发射机进入电气空闲

- Tx_L0s.Idle:在这个子状态,发射机保持电气空闲,直到被指示切换状态

- Tx_L0s.FTS:在这个子状态,发射机发送 FTS 有续集,发送的 FTS 数量是链路对端在其 TS 有序集合中在导致 L0 的最后一个训练序列中公布的 N_FTS 值

接收机也有三个子状态:

- Rx_L0s.Entry:当接收机接收到 EIOS 后进入此子状态,前提是它支持 L0s 并且尚未定向到 L1 或 L2。

- Rx_L0s.Idle:接收机处于电气空闲模式,等待退出电气空闲的指示。

- Rx_L0s.FTS:在此子状态,接收机退出电气空闲,试图在随后的比特流(实际上是 FTS 有续集)重新建立比特锁定和字符锁定或块锁定。

L1

相比于 L0s,L1 更加节省功耗,相应的退出延迟更大。L1 状态与 L0s 的不同之处还在于它影响链路的两个方向。

L1 有两个子状态:

- L1.Entry:为了使上游端口进入这种状态,必须向其链路对端发送进入 L1 的请求,一旦接收到 L1 请求确认,上行端口就进入 L1.Entry 子状态。为了使下游端口进入此状态,必须从上游端口接收 L1 输入请求,并对该请求发送确认响应。然后,下游端口等待接收 EIOS,并使其接收 Lane 上的电压下降到电气空闲,下游端口进入 L1 入口子状态。

- L1.Idle:在此子状态期间,变送器保持在电气空闲。

L2

L2 是功耗更低的状态。当上行端口的设备处于 D3Cold 电源状态并且适当的链路握手已经完成时,电源管理软件指示上行端口启动进入 L2。

在 L2 时,主供电(Main Power)被关断,只有辅助电源开启。

L2 有两个子状态:

- L2.Idle:要进入此子状态,链路上的两个端口之间必须已经进行了所有必要的握手过程,并且端口已经发送和接收了所需的 EIOS。

- L2.TransmitWake:在此子状态期间,发射器将至少在 Lane 0 上发送 Beacon。需要注意,此状态仅适用于上游端口,因为只有它们才能发送 Beacon。

Hot Reset

此状态的目的是允许使用带内信令将配置的链路和相关的下游设备进行复位操作。

Disable

被禁用的链路处于电气空闲状态,不必保持直流共模电压。软件通过在设备的链路控制寄存器中设置 Link Disable 位来启动此操作,然后设备发送 TS1(Link Disable 比特被置位)。

Loopback

Loopback 状态是一种测试和调试功能,在正常操作过程中不使用。充当环回主机的设备可以通过发送 TS1(Loopback 比特被置位),将链路伙伴置于环回从机模式。

4.3 Retimers

随着 PCIe 链路速度越来越快,信号衰减变得越来越大。为解决这个问题,有三种解决方案:高端的 PCB 板,Redriver 芯片,Retimer 芯片。

Redriver 本质上是通过信号放大来提升信号的高频分量,抵消链路上的衰减。Redriver 不涉及到任何协议相关的内容,所以链路两端的 PCIe 设备是无法感知到 Redriver 存在的。

Retimer 是一种模拟/数字混合芯片,其原理是使用内部的时钟恢复电路,重新定时输入信号以消除时钟偏移和抖动,并校正信号的相位和时间偏差(jitter)。它可以延长接口的传输距离并提高信号质量。Retimer 不仅会在 Rx 端实现 CTLE 和 DFE,还会在 Tx 端实现相应的均衡功能。因此 Retimer 能够比 Redriver 更好的降低链路物理损耗。但是,复杂的 Retimer 会增加链路延迟。Retimer 涉及到协议相关内容,本节正是描述 Retimer。链路两端的 PCIe 设备是可以感知到 Retimer 存在的。

Retimer 与 SoC 设计关系不大,略过。

4.4 动态带宽变化

PCIe 协议允许在运行时改变链路速率和宽度。比如,在性能优先时,使用最高的速率和最宽的 Lane 数;在功耗优先时,使用较低的速率和一部分 Lane。

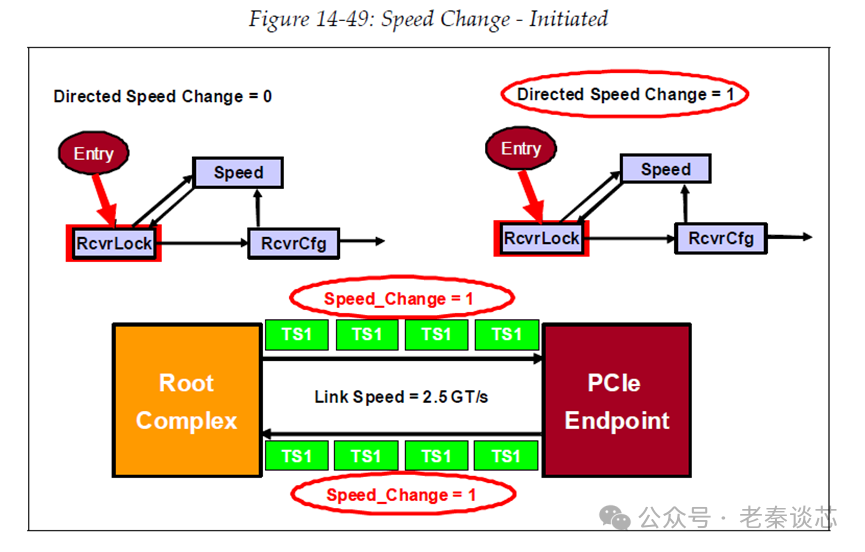

改变链路速率或链路宽度会造成链路重新训练。如果在链路处在 L0 状态时改变速率,发起端的 LTSSM 会发送 TS1,随后链路两端的端口的 LTSSM 都进入 Recovery 状态,当速率改变后再返回 L0 状态。

类似的,改变链路宽度的话,发起端的 LTSSM 开始发送 TS1,随后链路两端的端口的 LTSSM 都进入 Recovery 状态在进入 Configuration 状态,链路宽度改变后再返回 L0。

接下来分开分析。

4.4.1 动态链路速率变化

下图是 LTSSM 的状态转换图。在 Gen1 中,在 Polling 状态完成速率变换;在 Gen2 中,在 Recovery 状态完成速率变换。

TS1 的 Byte 4 是关于速率的指示,其中的 Bit 1-3 是支持的速率;Bit 6 的含义取决于是上游端口还是下游端口,以及 LTSSM 处于的状态,“Autonomous“表示出于自身硬件特定原因而非可靠性问题而要求进行此更改;Bit 7 被上行端口用来请求速度改变。在 TS2 中,Bit 6 的含义有一些不同。

注意,下图是 Gen 3 的 TS1/2 格式。在 Gen 5 中,Byte 4 的 Bit 4/5 用来指示更高速率。

速率变化必须由上游端口启动。下图是一个从 2.5GT/s 变换到 5.0GT/s 的例子。该例子中 EP 有一个上游端口,RC 有一个下游端口。下游端口的 LTSSM 进入 Recovery(Recovery.RcvrLock)状态,发送 TS1;下游端口接收到 TS1,也进入 Recovery,并返回 TS1。

当上游端口接收到下游端口返回的 TS1,进入 Recovery.RcvrCfg 状态,开始发送 TS2.下游端口监测到 TS2,进入 Recovery.RcvrCfg,返回 TS2。

两个端口监测到连续的 8 个 TS2,进入 Recovery.Speed。

一旦达到 Recovery.Speed 子状态,链路在两个方向上都处于电气空闲状态,速度变化发生在内部。选择的速度将是 TS1 和 TS2 的字段中指定的速度,在本例中是 5.0GT/s。随后,链路两端都转换回 Recovery.RcvrLock,并通过再次发送 TS1 退出电气空闲。

当硬件决定变换速率时,软件不能控制,但是可以通过控制寄存器限制或禁用此功能。

4.4.2 动态链路宽度变化

改变链路速度的相同基本操作也可以用于改变链路宽度,尽管顺序稍微复杂一些,因为涉及更多的 LTSSM 步骤。

下面是链路宽度改变的例子。

物理层是 PCIe 中最复杂和繁琐的部分,spec 中所占篇幅最多。限于篇幅和个人能力,很多内容只是简单介绍一点,甚至有的部分直接跳过了。

【待续】

END

作者:老秦谈芯

文章来源:老秦谈芯

推荐阅读

更多 IC 设计干货请关注IC 设计专栏。欢迎添加极术小姐姐微信(id:aijishu20)加入技术交流群,请备注研究方向。